# **Introduction to the Transistor**

**Purpose:** Demonstrate the current-controlled current source nature of the transistor, and investigate its three operating regions — cutoff, active and saturated.

### **Equipment Required**

- 1 Digital Multimeter

- 1 Triple Power Supply

- 1 Protoboard

- 1 2N3904 NPN Transistor

- 1  $1k\Omega$  Resistor

- 1  $100k\Omega$  Resistor

- 1  $10k\Omega$  Potentiometer

### **Prelab**

Read Section 4-3 in the textbook on transistors. Assume the transistor you will be using has a  $\beta$  of 200, and threshold voltage  $V_{\gamma}$  = 0.7V. The transistor will enter the active region when  $v_{in}$  reaches the turn-on voltage  $V_{\gamma}$ . For the circuit of Fig. 1, calculate the value of  $v_{in}$  that will cause the transistor to enter saturation.

## **Procedure**

#### 1. Build the circuit

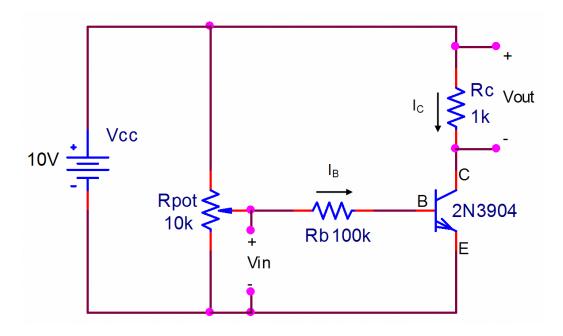

Figure 1

- a. Adjust the power supply  $V_{cc}$  so that it produces +10 V. Turn off the power supply.

- b. Measure and record the actual value of the  $1k\Omega$  and  $100k\Omega$  resistors that will be used in your circuit.

#### Caution

The transistor, like any semiconductor device, can be destroyed by over-current, overvoltage or static discharge. Over-current conditions are usually due to a wiring error. Over-voltage occurs when the power supply voltage exceeds the voltage rating for the device. These conditions can be avoided by ensuring you are using the proper device. and double-checking the circuit layout to catch — and correct — wiring errors. In the laboratory, damage from static discharge is often controlled by the use of grounded antistatic mats on the floor and the work surface. Manufacturers of ESD (electro-static discharge) sensitive devices recommend the use of a grounded wrist strap when working on sensitive electronics. You can help avoid damage from static discharge by touching an earth ground before picking up a semiconductor device. Earth grounds are available throughout a modern circuits lab, in the form of any metal case on a grounded instrument. Some power supplies provide a ground lug (or jack) separate from the negative side of the supply. The ground lug provides a good quality connection to earth ground through the third wire (round pin) on the AC power cord. Touching the metal portion of this ground lug will discharge any static electricity you have accumulated and significantly reduce the likelihood of damaging static-sensitive components.

- c. On a protoboard, build the circuit of Fig. 1. Turn on the power supply and adjust the potentiometer so that  $v_{out}$  is 5V.

- d. The voltage across the collect-emitter junction  $v_{ce}$  of the transistor is a good indicator of the present operating mode. Table 1 summarizes how to use the  $v_{ce}$  to determine the mode. In your journal, use the measured values of  $V_{cc}$  and  $v_{out}$  to write a KVL loop equation around the collector-emitter side of your circuit. Solve for  $v_{ce}$ . Use the equations in Table 1 to determine the operating mode.

| Table I           |                       |

|-------------------|-----------------------|

| Operating<br>Mode | Value of $v_{ce}$     |

| Cut-off           | $v_{ce} = V_{cc}$     |

| Active            | $0 < v_{ce} < V_{cc}$ |

| Saturated         | $v_{ce} = 0$          |

Measure  $v_{ce}$  and compute the percent error between the computed and measured values of  $v_{ce}$ .

# 2. Measure the $\beta$ of the transistor

- a. With  $v_{out}$  still at 5V, measure the voltage across  $R_B$ . Use Ohm's Law and the measured resistance values for  $R_B$  and  $R_C$  to compute  $i_B$  and  $i_C$ . Compute the forward current gain,  $\beta$ , from the dependent source equation for the transistor,  $i_C = \beta i_B$ . Record this empirically derived value for  $\beta$  in your lab journal.

- b. The  $\beta$  value is difficult to precisely control during the manufacturing process. Furthermore,  $\beta$  is subject to drift with time and temperature. The following procedure will demonstrate the dependence of  $\beta$  on the temperature of the transistor. Adjust  $v_{in}$  so the transistor is operating in the active region. While observing  $v_{out}$ , warm the transistor by pinching the package between your thumb and forefinger. If  $v_{out}$  does not change, ask someone with warm hands to help you. How is  $\beta$  related to the temperature of the transistor?

- c. Prepare a four-column table in your lab journal to record about thirty data points, labeling the columns  $v_{in}$ ,  $v_{out}$ ,  $v_{be}$  and  $v_{ce}$ . To acquire this data you'll vary  $v_{in}$  by adjusting the potentiometer. For  $v_{in}$  over the range from 0 to 1.5 volts, take data at intervals of about 0.25 volts (0V, 0.25V, 0.5V, etc.). For  $v_{in}$  from 1.5V to 10V, take data at 0.5V intervals.

#### 3. Plot the transfer characteristics

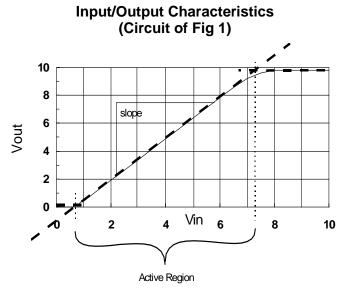

a. Use Excel (or similar) to graph the data you collected. Place  $v_{in}$  on the x axis, and plot three curves,  $v_{out}$ ,  $v_{be}$  and  $v_{ce}$ as functions of  $v_{in}$ . Your graph should be similar to the one shown in Fig. 2, but will also show  $v_{be}$  and  $v_{ce}$ . If enough data points were collected, the plot will show that the transitions between cutoff and active, and between active and saturated are somewhat rounded. Fit straight lines (manually if you wish) to each of the three operating modes for

Figure 2

the  $v_{out}$  data. The two intersections of these three straight lines represent the best approximation of the transition from cutoff mode to active mode, and from active mode to saturated mode. Draw a vertical line from the top to the bottom of your graph at each of these two intersections. Label the mode of operation for each of the three regions created by these lines.

### Conclusion

1. If one ignores the cutoff and saturated regions of the plot in part 3a one can fit a straight line in the active region that can be represented by an equation in the point-slope form, y=mx+b (where x equals  $v_{in}$  and y equals  $v_{out}$ ). Provide a mathematical derivation (hint: use  $i_C=\beta i_B$ , and Ohm's law) that shows  $\beta$  is related to the slope of the line in the active region by the equation:

$$\beta = \frac{mR_B}{R_C}$$

- 2. The y-intercept (b in the point-slope form) offsets the line from the origin. Write an equation for b in terms of the variables used in this circuit.

- 3. Use Excel's line fit routine to compute the slope and y-intercept of the line in the active region of the transistor input/output characteristics plot for your particular transistor. (You may want to copy your data set to a new sheet and then delete those portions that are affected by the cutoff and saturated regions of the I/V characteristics.) Using the measured slope and Eq. (1), calculate the average  $\beta$ . Does this  $\beta$  agree with the  $\beta$  measured in Procedure 2a of this lab? Use the computed value of b and the equation for b to determine an average  $v_{be}$  for this transistor. Does this agree well with the  $v_{be}$  found graphically in Procedure 3a?

- 4. Draw three schematic diagrams for the circuit of Fig. 1, one for each operating mode, however in place of the transistor draw the appropriate large-signal transistor model for that mode. For all three of these circuits write two KVL loop equations, one for the base-emitter side (which will include the voltage across  $R_B$ ) and one for the collector-emitter side of the circuit (which includes the voltage across  $R_C$ ).